# seL

The C Kernel Bitfield DSL

## Lyrabird

Simulation for Verification Modelling ARM

# Probability & Security

Side Channels Remote Exploits pGCL

## Projects

Vlibc Opportunistic Verification

Questions

# 10 Years of Trustworthy Systems

David Cock

July 29, 2014

# Outline

David Cock

# seL4

The C Kernel Bitfield DSL

# Lyrebird

Simulation for Verification Modelling ARM

Probability &

Side Channels Remote Exploits pGCL

# Projects

Vlibc Opportunistic Verification

Ouestions

1 seL4 The C Kernel Bitfield DSL

- 2 Lyrebird Simulation for Verification Modelling ARM

- 3 Probability & Security Side Channels Remote Exploits pGCL

- 4 Projects Vlibc Opportunistic Verificatio

- 6 Questions

## Lyrebird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Projects

Vlibc Opportunistic

Questions

# seL4

First ever verified kernel.

- Writen in C high-performance.

- Verified in Isabelle/HOL.

# seL4

The C Kernel Bitfield DSL

## Lyrebird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

## Projects

Vlibc Opportunistic

Ouestions

# seL4

First ever verified kernel.

- Writen in C high-performance.

- Verified in Isabelle/HOL.

- Open source from yesterday!

http://sel4.systems

Side Channels

Remote

Exploits pGCL

Projects

Vlibc Opportunistic Verification

Questions

The C kernel implements the high-level specification.

- Initial implementation 2 weeks.

- Small 8,700 lines.

- Fast 224cyc one-way IPC.

- DSL automation bitfields.

sel

The C Kernel Bitfield DSL

Lyrabird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Projects

Vlibc Opportunistic Verification

0 .:

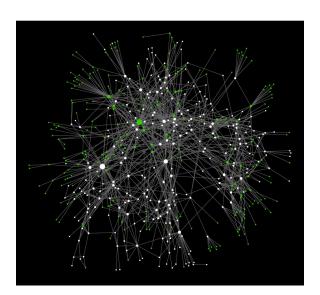

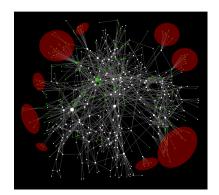

# The seL4 Call Graph

seL

The C Kernel Bitfield DSL

Lyrabird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Projects

Vlibc Opportunistic Verification

Questions

# The seL4 Call Graph

## seL

The C Kernel Bitfield DSL

## Lyrebird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

## Project

Vlibc Opportunistic Verification

Questions

- 573 functions.

- Not modular No SCCs..... except those leaves.

## sel

The C Kernel Bitfield DSL

### Lyrebird

Simulation for Verification Modelling ARM

# Probability & Security

Side Channels Remote Exploits pGCL

## Project

Vlibc Opportunistic Verification

Question

- 573 functions.

- Not modular No SCCs. . . . . except those leaves.

- 198 of these: 35% of functions, 16% of LOC.

## and /

The C Kernel

## Lvrebird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

## Project

Vlibc Opportunistic Verification

Questions

- 573 functions.

- Not modular No SCCs. . . . . except those leaves.

- 198 of these: 35% of functions, 16% of LOC.

- Generated and proved automatically from a DSL.

## seL4

The C Kernel Bitfield DSL

# Lyrebird

Simulation for Verification Modelling ARM

# Probability & Security

Side Channels Remote Exploits

# pGCL Project

Vlibc Opportunistic Verification

0 .:

```

DSL:

```

```

base 32 block B { padding 3 field Y 13 field Z 16 }

```

The C Kernel

Lyrebird Simulation for Verification Modelling ARM

Probability & Security

Side Channels

Remote

Exploits

pGCL Project:

Vlibc Opportunistic Verification

Ouestions

```

DSL:

```

```

base 32 block B { padding 3 field Y 13 field Z 16 } \,

```

• C:

```

static inline void

B_ptr_set_X(B_t *B_ptr, uint32_t v) {

B_ptr->words[0] &= ~0x1fff0000;

B_ptr->words[0] |= (v<<16)&0x1fff0000;

}</pre>

```

# seL4 The C Kernel

Bitfield DSL

Simulation for Verification Modelling ARM

Probability & Security

Side Channels

Remote Exploits pGCL

Project

Vlibc Opportunistic Verification

Ouestions

DSL:

```

base 32

block B { padding 3 field Y 13 field Z 16 }

```

C:

```

static inline void

B_ptr_set_X(B_t *B_ptr, uint32_t v) {

B_ptr->words[0] &= ~0x1fff0000;

B_ptr->words[0] |= (v<<16)&0x1fff0000;

}</pre>

```

HOL:

```

B_lift \ B \equiv (B_CL.X_CL = ((index \ (B_C.words_C \ B) \ 0) >> 16) \ AND \ 8191, \\ B_CL.Y_CL = ((index \ (B_C.words_C \ B) \ 0) >> 0) \ AND \ 65535)

```

Lyrebird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Projects

Vlibc Opportunistic

Questions

# Automation Helps!

- 35% of the functions in seL4 were proved automatically.

- The tool is now widely used in NICTA.

- It's used by engineers, not formal methods people.

- Many features not mentioned: tagged unions, multilevel decoding, . . . .

Security

Side Channels

Remote

Exploits

pGCL Projects

Vlibc Opportunistic Verification

Questions

# For more see:

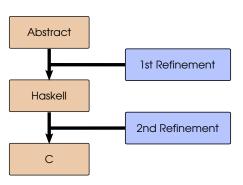

- Running the manual: An approach to high-assurance microkernel development, Haskell Workshop '06.

- Bitfields and tagged unions in C: verification through automatic generation, VERIFY'08.

- Secure microkernels, state monads and scalable refinement, TPHOLS'08.

- Mind the gap: A verification framework for low-level C, TPHOLS'09.

- seL4: Formal verification of an OS kernel, SOSP'09

# Outline

# David Cock

# seL4

The C Kernel Bitfield DSL

# Lyrebird

Simulation for Verification Modelling ARM

Probability &

Side Channels Remote Exploits pGCL

# Projects

Vlibc Opportunistic Verification

Ouestions

1 seL4 The C Ke

Bitfield DSL

2 Lyrebird Simulation for Verification Modelling ARM

- 3 Probability & Security

Side Channels

Remote Exploits

pGCL

- 4 Projects

Vlibc

Opportunistic Verification

- 6 Questions

# seL

The C Kernel Bitfield DSL

# Lyrebird

Simulation for Verification Modelling ARM

# Probability & Security

Side Channels Remote Exploits pGCL

## Project

Vlibc Opportunistic

Questions

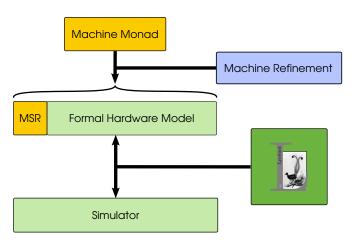

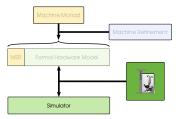

- A DSL for CPU/system modelling.

- High performance simulator.

- Automatic formal model.

- Used to prototype seL4.

The C Kernel Bitfield DSL

Simulation for Verification Modelling ARM

Probability &

Side Channels Remote Exploits

pGCL

Vlibc Opportunistic Verification

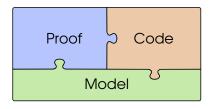

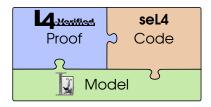

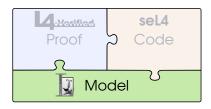

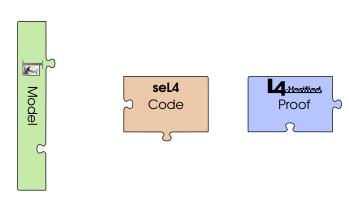

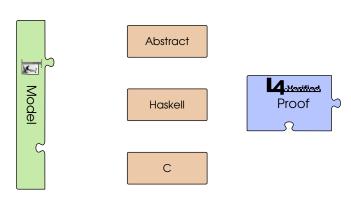

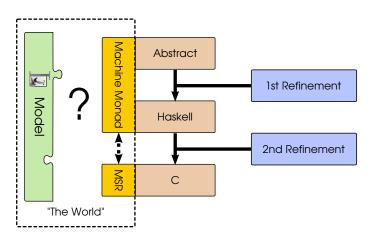

Program proof is important, but there's more to do.

The C Kernel Bitfield DSL

Simulation for Verification Modelling

ARM

Probability &

Side Channels Remote Exploits

pGCL

Vlibc Opportunistic Verification

Program proof is important, but there's more to do.

The C Kernel Bitfield DSL

Simulation for Verification

Modelling ARM

Probability Security

Side Channels Remote Exploits

pGCL Project

Vlibc Opportunistic Verification

Questions

Program proof is important, but there's more to do.

Any statement "P is True" is incomplete: It must be read as ", under Q - my model of the world".

# Goal

Development outcomes: program, proof and model.

The C Kernel Bitfield DSL

Simulation for Verification

Modelling ARM

Probability &

Side Channels Remote Exploits

pGCL

Vlibe

Opportunistic Verification

Program proof is important, but there's more to do.

# seL4 The C Kernel

Bitfield DSL

# Simulation for

Verification Modelling ARM

Probability of

Side Channels Remote Exploits

pGCL Project:

> Vlibc Opportunistic Verification

0 .:

Program proof is important, but there's more to do.

Our approach is a language framework: Lyrebird.

10 Years of Trustworthy Systems

# David Cock

The C Kernel Bitfield DSL

Simulation for Verification

Modelling ARM

Probability &

Side Channels Remote Exploits pGCL

# Projects

Vlibc

Opportunistic Verification

# seL

The C Kernel Bitfield DSL

## Lyrebire

Simulation for Verification Modelling

Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

## Project

Vlibc

Opportunistic Verification

Ouestion

## seL4

The C Kernel Bitfield DSL

## Lyrebird

Simulation for Verification

Modelling ARM

Probability &

Side Channels Remote

Exploits pGCL

Project:

Vlibc

Opportunistic Verification

Ougetions

The C Kernel Bitfield DSL

Simulation for Verification

Modelling ARM

Probability &

Side Channels Remote Exploits pGCL

Vlibc Opportunistic Verification

The C Kernel Bitfield DSL

Simulation for Verification

Modelling ARM

Probability &

Side Channels Remote Exploits pGCL

Vlibc

Opportunistic Verification

# seL4

The C Kernel Bitfield DSL

# Lyrebird

Simulation for Verification Modelling

# Modelling ARM

Probability & Security

Side Channels Remote Exploits

# pGCL Project

Vlibe

Opportunistic Verification

Questions

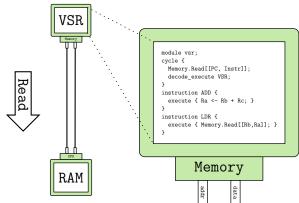

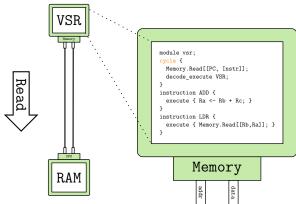

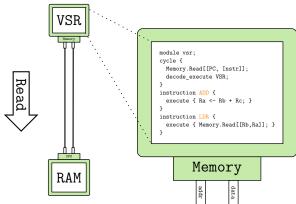

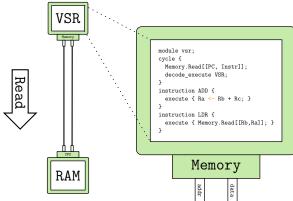

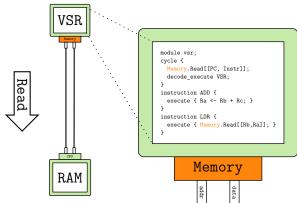

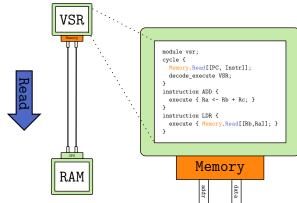

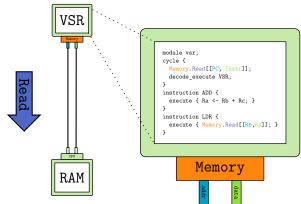

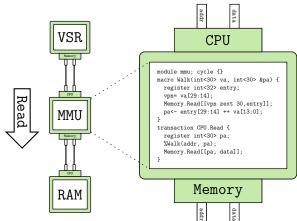

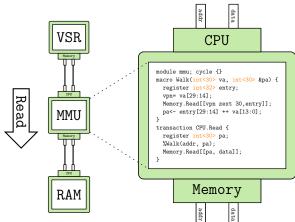

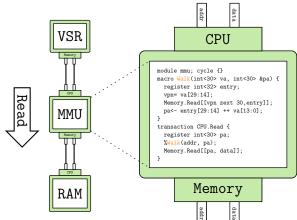

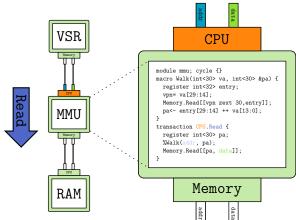

A simple model of a CPU connected to RAM.

The C Kernel

Lyrebird

Simulation for

Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Projects

Vlibc Opportunistic Verification

Ougetions

Modules are written in Lyrebird.

The C Kernel

Lyrebird

Simulation for

Modelling ARM

Probability &

Side Channels Remote

Exploits pGCL

Project

Vlibc Opportunistic

Questions

The cycle specifies asynchronous behaviour.

The C Kernel

Lyrebird

Simulation for

Modelling ARM

Probability &

Side Channels Remote Exploits

pGCL Project:

Vlibe

Opportunistic Verification

Questions

Modules export instructions.

The C Kernel Bitfield DSL

Lyrebird

Simulation for Verification

Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic

Questions

All behaviour is built from register transfers.

The C Kernel

Lyrebird

Simulation for Verification

Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project:

Vlibc Opportunistic

Ouestions

Modules are linked by interfaces.

The C Kernel

Lyrebird

Simulation for Verification Modelling

Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project:

Vlibc Opportunistic

Ouestions

Interfaces define transactions.

The C Kernel

Lyrebird

Simulation for Verification Modelling ARM

Probability &

Side Channels

Remote

Exploits

pGCL

Projects

Vlibc Opportunistic

Ouestions

Transactions access the datapath.

The C Kernel Bitfield DSL

Simulation for Verification

# Modelling ARM

Probability &

Side Channels Remote Exploits

# pGCL

Vlibc

Opportunistic Verification

Interfaces and modules allow different implementations.

The C Kernel Bitfield DSL

Lyrebird

Simulation for Verification

Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic

Ouestions

Lyrebird can also be used to model devices.

The C Kernel

Lyrebird

Simulation for Verification

Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic

Ouestions

Register types have explicit width.

The C Kernel

Lyrebird

Simulation for Verification

Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Projects

Vlibc Opportunistic

Questions

Type-checked macros minimize duplication.

The C Kernel

Lyrebird

Simulation for Verification

Modelling ARM

Probability & Security

Side Channels

Remote Exploits

Project

Vlibc Opportunistic

Ouestions

Transactions are implemented by modules.

Lyrebird

Simulation for Verification

Modelling ARM

Probability

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic

Questions

### ARMv6 Model

- We have an ARMv6 user-level integer instruction model.

- Floating-point and vector operations are excluded.

- The complete model is approximately 1600 lines.

- We used it to validate the seL4 Haskell prototype.

The C Kernel Bitfield DSL

Simulation for Verification Modelling

## ΔRM

Side Channels Remote Exploits

# pGCL

Vlibe Opportunistic Verification

### Simulation

Register transfer is easy to simulate.

The simulator is portable and fast — 10MIPS for ARMv6 user.

The output is a single C module;

It is easily incorporated into larger simulations.

# Further Reading

### David Cock

### seL4

The C Kernel Bitfield DSL

### Lyrebird

Simulation for Verification Modelling

### ARM

### Probability &

Side Channels Remote Exploits pGCL

### Project

Vlibc Opportunistic Verification

Questions

### For more see:

• Lyrebird — assigning meanings to machines, SSV'10

## Outline

### David Cock

### seL4

The C Kernel Bitfield DSL

### Lyrebire

Simulation for Verification Modelling ARM

## Probability & Security

Side Channels Remote Exploits pGCL

### Project

Vlibc Opportunistic

Ouestions

The C Kerne

2 Lyrebird

Simulation for Verification

Modelling ARM

- 3 Probability & Security

Side Channels

Remote Exploits

pGCL

- 4 Projects

Vlibc

Opportunistic Verification

- 6 Questions

#### . . .

The C Kernel Bitfield DSL

#### Lyrebird

Simulation for Verification Modelling ARM

Probability Security

#### Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic

.

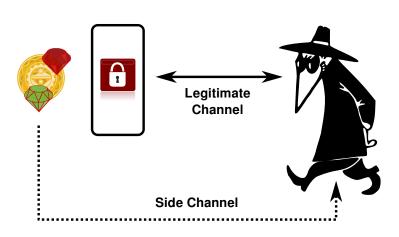

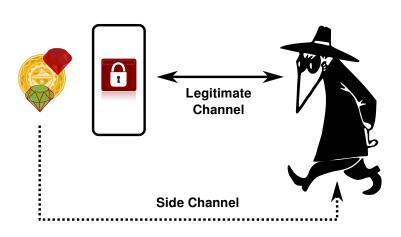

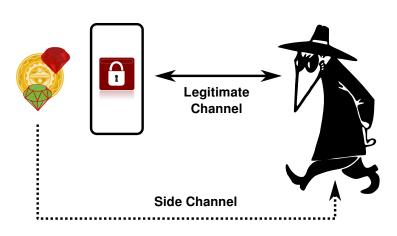

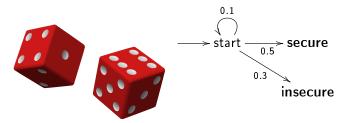

### The Problem

The attacker tries to guess the lock combination.

#### ool /

The C Kernel Bitfield DSL

#### Lvrebird

Simulation for Verification Modelling ARM

Probability & Security

#### Side Channels Remote Exploits pGCL

#### Project

Vlibc Opportunistic

Verification

Questions

### The Problem

After n tries he's locked out.

#### seL4

The C Kernel Bitfield DSL

### Lyrebird

Simulation for Verification Modelling ARM

Probability Security

#### Side Channels Remote Exploits pGCL

#### Project

Vlibc Opportunistic

Questions

### The Problem

Every guess leaks something about the combination.

#### sel /

The C Kernel Bitfield DSL

#### Lyrabird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

### Project

Vlibc Opportunistic Verification

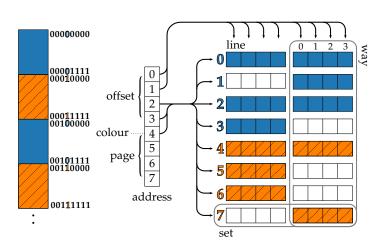

### The Cache Channel

The C Kernel Bitfield DSL

#### Lynnalstad

Simulation for Verification Modelling ARM

Probability & Security

#### Side Channels Remote Exploits pGCL

### Project

Vlibc Opportunistic Verification

0 .:

### The Cache Channel

• It's easy to spot a cache miss.

The C Kernel Bitfield DSL

Simulation for Verification Modelling ARM

Probability &

#### Side Channels Remote Exploits pGCL

Vlibe Opportunistic Verification

### The Cache Channel

- It's easy to spot a cache miss.

- Cache contention forms a channel.

seL4

The C Kernel

Bitfield DSL

Lyrebird

ARM

Simulation for Verification

Probability Security

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic Verification

Questions

### The Cache Channel

- It's easy to spot a cache miss.

- Cache contention forms a channel.

- This is a big problem in crypto e.g. AES.

10 Years of Trustworthy Systems

#### David Cock

seL4

The C Kernel Bitfield DSL

Lyrebird

Simulation for Verification Modelling ARM

Probability of Security

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic Verification

Questions

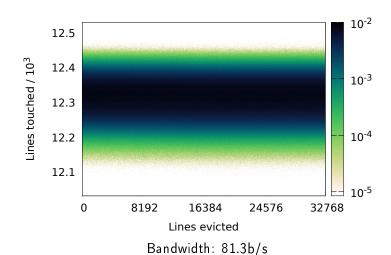

### The Cache Channel

- It's easy to spot a cache miss.

- Cache contention forms a channel.

- This is a big problem in crypto e.g. AES.

We ran a large empirical evaluation:

- 3 channels, 2 countermeasures and 5 platforms.

- 6 months of observations

- Integrated with regression tests.

10 Years of Trustworthy Systems

### David Cock

The C Kernel

Lyrebir

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic Verification

Questions

| Processor     | iMX.31      | E6550     | DM3730    | AM3358    | Exynos4412 |

|---------------|-------------|-----------|-----------|-----------|------------|

| Manufacturer  | Freescale   | ln t el   | TI        | TI        | Samsung    |

| Architecture  | ARM∨6       | ×86-64    | ARMv7     | ARMv7     | ARM∨7      |

| Core type     | ARM1136JF-S | Conroe    | Cortex A8 | Cortex A8 | Cortex A9  |

| Released      | 2005        | 2007      | 2010      | 2011      | 2012       |

| Cores         | 1           | 2         | 1         | 1         | 4          |

| Clock rate    | 532 MHz     | 2.33 G Hz | 1 G Hz    | 720 MHz   | 1.4 G Hz   |

| Timeslice     | 1 ms        | 2 ms      | 1 ms      | 1 ms      | 1 ms       |

| RAM           | 128 MiB     | 1024 MiB  | 512 MiB   | 256 MiB   | 1024 MiB   |

| L1 D-cache    |             |           |           |           |            |

| size          | 16 KiB      | 32 KiB    | 32 KiB    | 32 KiB    | 32 KiB     |

| in d e×       | virtual     | physical  | v irtu al | v irtu al | virtual    |

| tag           | physical    | physical  | physical  | physical  | physical   |

| line size     | 32 B        | 64 B      | 64 B      | 64 B      | 32 B       |

| lines         | 512         | 512       | 512       | 1024      | 512        |

| associativity | 4           | 8         | 4         | 4         | 4          |

| sets          | 128         | 64        | 128       | 128       | 256        |

| L2 cache      |             |           |           |           |            |

| size          | 128 KiB     | 4096 KiB  | 256 KiB   | 256 KiB   | 1024 KiB   |

| line size     | 32 B        | 64 B      | 64 B      | 64 B      | 32 B       |

| lines         | 4096        | 65,536    | 4096      | 4096      | 32,768     |

| associativity | 8           | 16        | 8         | 8         | 16         |

| sets          | 512         | 4096      | 512       | 512       | 2048       |

| colours       | 4           | 64        | 8         | 8         | 16         |

|               |             |           |           |           |            |

Table: Experimental platforms.

10 Years of Trustworthy Systems

### David Cock

The C Kernel

Lyrebird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic Verification

Questions

| Processor     | iMX.31      | E6550     | DM3730    | AM3358    | Exynos4412 |

|---------------|-------------|-----------|-----------|-----------|------------|

| Manufacturer  | Freescale   | Intel     | TI        | TI        | Samsung    |

| Architecture  | ARM∨6       | ×86-64    | ARM∨7     | ARM∨7     | ARM∨7      |

| Core type     | ARM1136JF-S | Conroe    | Cortex A8 | Cortex A8 | Cortex A9  |

| Released      | 2005        | 2007      | 2010      | 2011      | 2012       |

| Cores         | 1           | 2         | 1         | 1         | 4          |

| Clock rate    | 532 MHz     | 2.33 G Hz | 1 G Hz    | 720 MHz   | 1.4 G Hz   |

| Timeslice     | 1 ms        | 2 ms      | 1 ms      | 1 ms      | 1 ms       |

| RAM           | 128 MiB     | 1024 MiB  | 512 MiB   | 256 MiB   | 1024 MiB   |

| L1 D-cache    |             |           |           |           |            |

| size          | 16 KiB      | 32 KiB    | 32 KiB    | 32 KiB    | 32 KiB     |

| in d e×       | virtual     | physical  | v irtu al | v irtu al | virtual    |

| tag           | physical    | physical  | physical  | physical  | physical   |

| line size     | 32 B        | 64 B      | 64 B      | 64 B      | 32 B       |

| lines         | 512         | 512       | 512       | 1024      | 512        |

| associativity | 4           | 8         | 4         | 4         | 4          |

| sets          | 128         | 64        | 128       | 128       | 256        |

| L2 cache      |             |           |           |           |            |

| size          | 128 KiB     | 4096 KiB  | 256 KiB   | 256 KiB   | 1024 KiB   |

| line size     | 32 B        | 64 B      | 64 B      | 64 B      | 32 B       |

| lines         | 4096        | 65,536    | 4096      | 4096      | 32,768     |

| associativity | 8           | 16        | 8         | 8         | 16         |

| sets          | 512         | 4096      | 512       | 512       | 2048       |

| colours       | 4           | 64        | 8         | 8         | 16         |

Table: Experimental platforms.

### seL4

The C Kernel Bitfield DSL

### Lvrebird

Simulation for Verification Modelling ARM

Probability & Security

#### Side Channels Remote Exploits

pGCL

Vlibe

Opportunistic

Questions

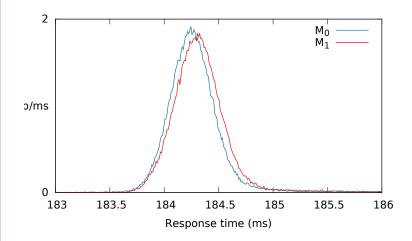

# Exynos4 Cache Channel

Bandwidth: 7.04kb/s

### sel /

The C Kernel Bitfield DSL

#### Constitution of

Simulation for Verification Modelling ARM

Probability & Security

#### Side Channels Remote Exploits pGCL

#### Project

Vlibc Opportunistic

0 11

# Cache Colouring

### seL4

The C Kernel Bitfield DSL

### Lyrebird

Simulation for Verification Modelling ARM

Probability &

#### Side Channels Remote Exploits

Remote Exploits pGCL

### Project

Vlibc Opportunistic

Questions

### Coloured Cache Channel

#### sel A

The C Kernel Bitfield DSL

### Lyrebir

Simulation for Verification Modelling ARM

Probability Security

### Side Channels Remote

Remote Exploits pGCL

### Projects

Vlibc Opportunistic Verification

Questions

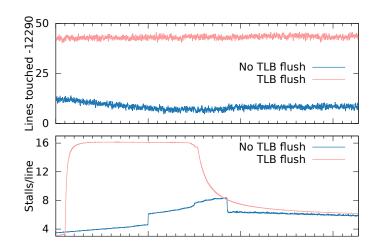

### Residual TLB Channel

Simulation for Verification Modelling ARM

Side Channels Remote Exploits pGCL

Vlibe Opportunistic Verification

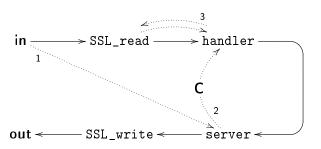

- This is a recent vulnerability in OpenSSL TLS.

- Runtime depends on unvalidated user input.

- Can be used as a decryption oracle.

- 'Fixed' with a constant-time algorithm.

- We reproduced the attack on seL4...

Lyrebi

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project:

Vlibc Opportunistic

Ouestions

This is a recent vulnerability in OpenSSL TLS.

- Runtime depends on unvalidated user input.

- Can be used as a decryption oracle.

- 'Fixed' with a constant-time algorithm.

- We reproduced the attack on seL4...

- ...and fixed it with better performance!

- Required no modifications to OpenSSL.

### ا ا د

The C Kernel Bitfield DSL

#### Lorenhied

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits

### pGCL Project:

Vlibc Opportunistic Verification

Questions

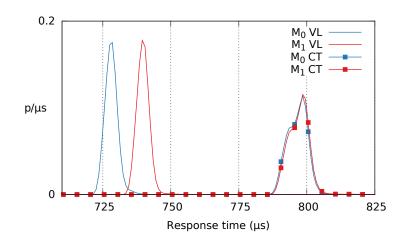

# The Lucky-13 Attack

### ool /

The C Kernel Bitfield DSL

#### 1000

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote

Remote Exploits pGCL

#### Project

Vlibc Opportunistic Verification

0 .:

### Intercontinental Attack

### Lyrebird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote

Exploits pGCL

### Project

Vlibc Opportunistic Verification

0 .:

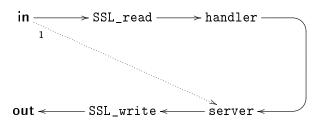

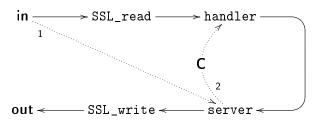

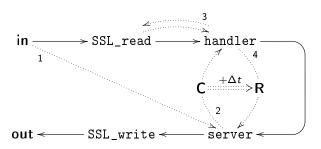

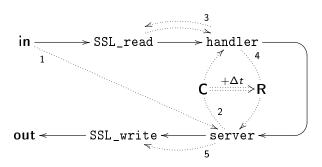

# Scheduled Delivery

$in \longrightarrow SSL\_read \longrightarrow handler -$

out <---- SSL\_write <---- server <----

network

TLS

### ا اه

The C Kernel Bitfield DSL

#### Lorenhied

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits

### pGCL

Project

Vlibc Opportunistic

0 .:

# Scheduled Delivery

network

TLS

### . . . .

The C Kernel Bitfield DSL

#### Lorenhied

Simulation for Verification Modelling ARM

Probability of Security

Side Channels Remote Exploits

### pGCL Project

Vlibc Opportunistic Verification

0.....

# Scheduled Delivery

network

TLS

#### --1

The C Kernel Bitfield DSL

#### Lorenteland

Simulation for Verification Modelling

Probability & Security

Side Channels Remote Exploits

## pGCL

Vlibc Opportunistic

.

# Scheduled Delivery

network

TLS

### بامه

The C Kernel Bitfield DSL

#### Lorenhied

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits

# pGCL

Vlibc Opportunistic

.

# Scheduled Delivery

network

TLS

### بامد

The C Kernel Bitfield DSL

#### Lorenhied

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits

### pGCL Project

Vlibc Opportunistic

0 11

# Scheduled Delivery

network

TLS

### بامم

The C Kernel Bitfield DSL

#### Large Island

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits

### pGCL Project:

Vlibc Opportunistic

Questions

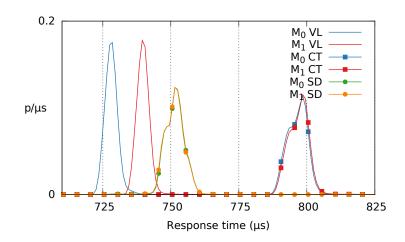

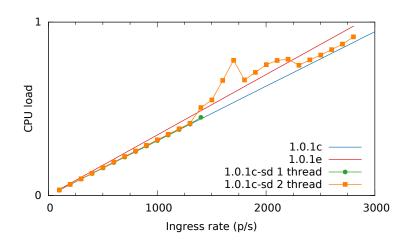

# Lucky-13 Mitigated

### 1.4

The C Kernel Bitfield DSL

#### 1000

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits

pGCL

Project

Vlibc Opportunistic Verification

Ouestions

### Load Performance

# Further Reading

### David Cock

### seL4

The C Kernel Bitfield DSL

#### Lyrebird

Simulation for Verification Modelling ARM

Probability of Security

Side Channels Remote Exploits

# pGCL

Vlibc Opportunistic

Questions

### For more see:

- Exploitation as an inference problem, AISEC,11.

- The Last Mile: An Empirical Study of Some Timing Channels on seL4, CCS'13.

### Lyrebird

Simulation for Verification Modelling ARM

Probability Security

Side Channels Remote Exploits pGCL

### Project

Vlibc Opportunistic Verification

Questions

# pGCL

- pGCL is a language of probabilistic automata.

- It models both demonic and probabilistic choice.

- My Isabelle/HOL formalisation is now in the Archive of Formal Proofs.

- Used to formally verify probabilistic security properties e.g. side channel leakage.

Lyrebird

Simulation for Verification Modelling ARM

Probability Security

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic Verification

Questions

### For more see:

- Verifying probabilistic correctness in Isabelle with pGCL, SSV'12

- From probabilistic operational semantics to information theory side channels with pGCL in isabelle, ITP'14

- pGCL for Isabelle, Archive of Formal Proofs, 2014

## Outline

### David Cock

### seL4

The C Kernel Bitfield DSL

### Lyrebird

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

### Projects

Vlibc Opportunistic Verification

Questions

# 1 seL4

The C Kerne Bitfield DSL

- 2 Lyrebird Simulation for Verification Modelling ARM

- 3 Probability & Security

Side Channels

Remote Exploits

pGCL

- 4 Projects Vlibc Opportunistic Verification

- 6 Questions

### ر امه

The C Kernel Bitfield DSL

### Lyrebird

Simulation for Verification Modelling ARM

Probability &

Side Channels Remote Exploits

pGCL Project

### Vlibe

Opportunistic

Questions

# Can We Verify the C Library?

### An open project:

- Work in a public repository.

- Code only accepted with proof.

- Self-contained student projects.

#### Lyrebird Simulation for

Verification Modelling ARM

Side Channels

Remote

Exploits

pGCL

Project

### Vlibc Opportunistic

Opportunist Verification

Questio

# Can We Verify the C Library?

### An open project:

- Work in a public repository.

- Code only accepted with proof.

- Self-contained student projects.

### Applications:

- Systems on a verified kernel.

- Library spec for symbolic execution (no tracing libc!).

- Verified compiler (CompCert) needs a verified runtime.

### Lyrebi

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project

Vlibc Opportunistic Verification

Questions

# Getting Value out of FM

You don't have to do seL4 to benefit from FM:

- Go for bang/buck.

- Focus on things likely to be wrong.

- Provide a toolset to programmers.

Lyrebi

Simulation for Verification Modelling ARM

Probability & Security

Side Channels Remote Exploits pGCL

Project:

Vlibc Opportunistic Verification

A ...

# Getting Value out of FM

You don't have to do seL4 to benefit from FM:

- Go for bang/buck.

- Focus on things likely to be wrong.

- Provide a toolset to programmers.

DSLs provide a convenient interface:

- We've seen examples: Bitfields, Lyrebird, . . .

- Match to tool to the job.

- Full formalism isn't exposed to programmers.

- Don't force everything into a single framework: provide tools!

## Outline

### David Cock

### sel 4

The C Kernel Bitfield DSL

#### Lyrebird Simulation for

Verification Modelling ARM

Security 8

Side Channels Remote Exploits pGCL

#### Projects

Vlibc Opportunistic Verification

Questions

### **1** seL4

The C Kerne Bitfield DSL

2 Lyrebird

Simulation for Verification

3 Probability & Security Side Channels Remote Exploits

4 Projects

Vlibc

Opportunistic Verification

6 Questions

#### seL4

The C Kernel Bitfield DSL

#### Lyrebird

Simulation for Verification Modelling ARM

### Probability & Security

Side Channels Remote Exploits

### pGCL Project

Vlibc Opportunistic Verification

Questions

# Questions?